## Bus Currents and Voltages when operating a Modular Multilevel Converter (M2LC) in Resonance Mode

Michael E. Aiello 9/21/2018

mailto:michael.e.aiello@comcast.net

Revision -

Revision History:

Revision – (9/21/18)

First draft.

## **Abstract**

The discussion of a proposed technique to produce DC or low frequency AD at the output of a *multilevel converter* (M2LC) was presented in <u>Operation of M2LC in Resonance Mode</u>.

The paper presented a simulation of one leg of a M2LC stack operating in a special mode that would force a resonance condition based on the values of the interphase inductance and link capacitor selected. The cited paper also presented operation of one M2LC stack under various load conditions.

In all simulations presented, the plus and minus bus was presented as a zero impedance volage set at fixed +/- 1000 volts DC of zero impedence. In reality, the implementation of a high voltage M2LC would not provide for an ideal condition such as this.

Any references to the operattion of a mult-phase configuration of the stack (say 3-phase) presented in the cited paper was created by superimposing seperate operating conditions for each phase. For example, one sumulation presented was an operating condition where Phase-A was connected to a +20 amp current source, and Phase-C was connected to a -20 amp current source (Phase-B was open). The resonance mode was set to *intermediate* (see Figure 43 of Operation of M2LC in Resonance Mode).

The purpose of this paper, is to gain some insight into the operation of a 3-phase M2LC in renonance mode, under a more realistic condition where impedance is present in both the plus and minus bus connections.

## Background

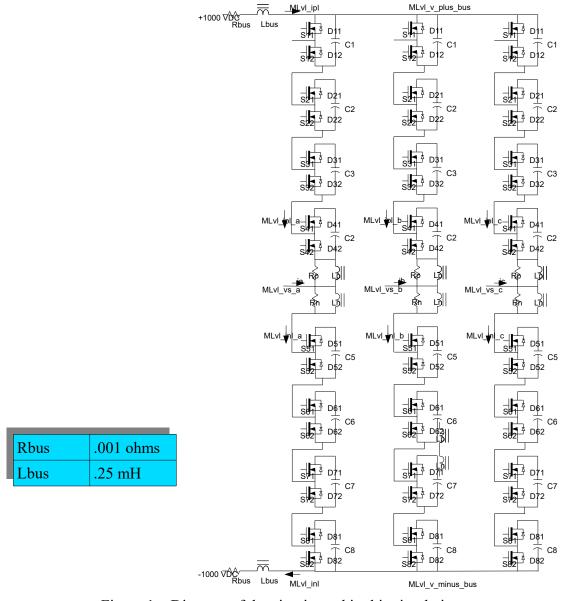

The diagram for the circuit used in this presentation is shown in Figure 1.

Figure 1 Diagram of the circuit used in this simulation.

The characteristics of each of the three M2LC stacks is identical to that presented in Figure 1 of  $\underline{\text{Operation of M2LC in Resonance Mode}}$ . However as shown here, three phases are connected to a common + and - DC bus with series impedance.

In <u>Operation of M2LC in Resonance Mode</u>, the single M2LC stack was simulated using a fixed time step of .00000064 seconds applied to 68 x 68 matrix. For this simulation, the addition of a concurrent operation of three phase using a single step calculation would involve a matrix size greater then 3\*68 x 3\*68. Using this type of approach like would be prohibitive to say the least.

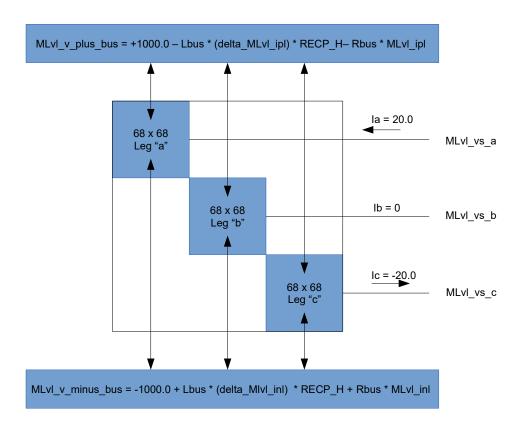

Instead, I choose a simpler method using two time steps per calculation. This is outlined in Figure 2.

Figure 2 Block diagram of method to determine the plus and minus bus voltages labeled MLvl\_v\_plus and MLvl\_v\_minus\_bus.

The simulation represented in Figure 2 is accomplished by *forking* three processes in Linux, one process for each 68 x 68 matrix describing the M2LC stack representing the legs of phases A, B, and C. Process number 1 (phase A) is set for the desired switching sequence with a +20 amp current source applied to the load connection (in this case **MLvl\_vs\_a**). A similar setup is done for process 2 (phase B) and process 3 (phase C). Note that the system is balanced (20 amps in and 20 amps out at the load connections).

All three processes are run for one time step wih H = .00000064 seconds, with RECP\_H equal to 1/H as shown in Figure 2. Then the bus plus and minus *leg* currents of all three stacks (labeled MLvl\_ipl\_<leg> and MLvl\_inl\_<leg> in Figure 1) are added to determine MLvl\_ipl and MLvl\_inl in Figure 2. From this information, the second step in executed (in the same time step) to determine MLvl\_v\_plus\_bus and MLvl\_v\_minus\_bus. The values MLvl\_v\_plus\_bus and MLvl\_v\_minus\_bus

are then fed back to each of the three processes in order calculate the states for the next time step.

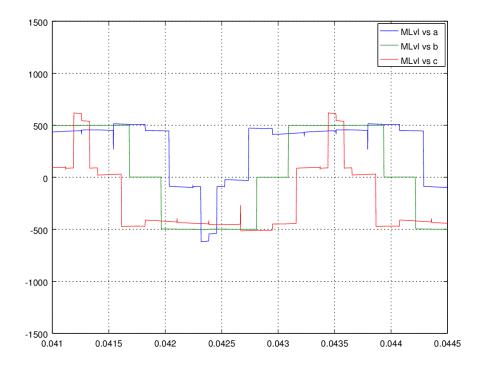

The modulation sequences for each stack (phase) as viewed form the load connections MLvl\_vs\_a, MLvl\_vs\_b and MLvl\_vs\_c are shown in Figure 3.

Figure 3 Modulation sequences viewed at load connections.

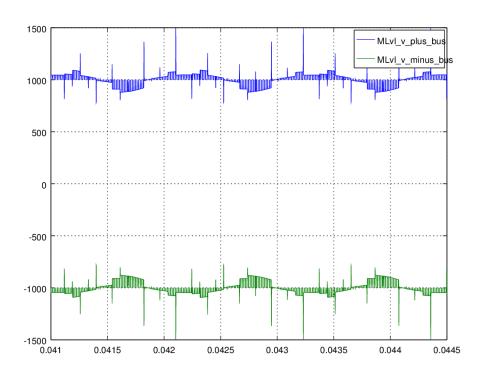

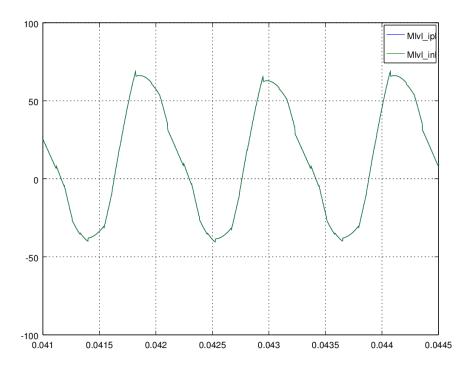

The resulting bus voltages and currents are shown in Figure 4 and Figure 5 respectively. The system is balanced as evident in Figure 5 where the current flowing in the plus bus is equal to the current flowing in the minus bus.

The discontinuities of the bus voltages shown in Figure 4 are due in part to simulation noise and the points where the change in bus current goes to zero due to short intervals where current *circulation* within the 3-phase bridge occures.

Figure 4 Simulated bus voltages for the system depected in Figure 1.

Figure 5 Simulated bus currents for the system depected in Figure 1.